三农快评

不到一天时间,母子两人先后被村干部等人认定为“精神病”送进了精神病医院。然而,记者的调查却显示这对母子很有可能是“被精神病”了!如果属实,这事还真是让人不寒而栗。

澎湃新闻5月22日报道,4月19日下午,湖北省恩施市屯堡乡杨家山村村民李和永被村委会、乡派出所、医院的人一起以治疗坐板疮为由,送进了当地一家医院的精神病房。当晚12点多,李和永母亲也被送进了同一家医院的精神科。

记者之所以怀疑他们“被精神病”,有这样几个原因。

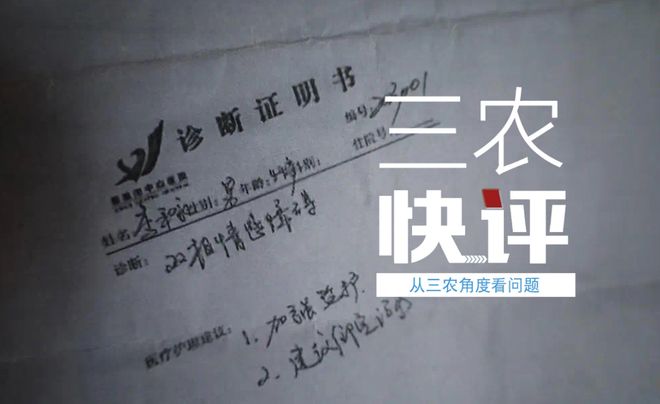

医院精神科负责人说,收治李和永的依据是当地提供的2023年5月筛查时,李和永的精神疾病诊断证明,以及当地反映李和永威胁要打村干部。对于这个证明,李和永说未接受过筛查,对此毫不知情。而且,按照规定,对于筛查时的诊断结果,到医院后还需要进一步复核,但复核到现在也没有做。对于威胁打人,医院精神科负责人表示,不认为李和永有伤害他人的危险。也就是说,李和永被认定为精神病人的这两个依据都有疑问,都不牢靠。 此外,记者走访调查了李和永的多位亲戚邻居,都表示他精神正常。

还有李和永的母亲,被认为是精神病人的一个重要依据是儿子被带走的当天半夜十二点,拿着砍刀到村委会疯狂砸门。记者求证时,村民说没听到李和永母亲砸门的事,村干部说有监控,但在维修,也拿不出证据。

从目前来看,能证明李和永与他的母亲是精神病人的证据,没有哪个是确切的。

让人们怀疑李和永母子“被精神病”,还有一个重要原因是李和永被带走的时间。李和永和其他6名村民,前几年因为涉田地纠纷打官司败诉,这两年一直在上访。李和永懂法律,是上访的主力。4月20日是他们准备要再次上访的时间,19日就发生了被带走的事。这很难不让人产生联想,当地是不是在对他上访进行打击报复?是不是通过这种手段阻止他上访?

李和永与他的母亲如果“被精神病”情况属实,那真有点让人不寒而栗。一个正常的人被迫和精神病人待在一起,说正常的话也会被诬为疯话,想要自证清醒还真不容易。有苦不能诉,有冤不能伸,时间一长,被变成真正的精神病人也不是不可能。更可怕的是,信访是公民的权力,即使过程当中有违法违规的行为,国家也有相应的法律法规给予纠治。如果是把上访人员轻易就变成“精神病人”来阻止上访,那人们还有什么安全感可言?

对于此事,截至5月23日的进展是恩施市已经成立调查组,后续情况将及时发布。我们期待恩施市能拿出一个有理有据、让人信服的调查结果。

三农快评——从三农角度看问题

聚焦“三农”领域大事、要事、急事、难事,权威跟踪“三农”领域热点、焦点、难点、重点话题,独家解析“三农”新闻事件,认真寻找新闻第二落点,用有速度的关注、有高度的站位、有态度的表达、有温度的关爱、有深度的见解回应社会关切。

作者丨中国三农发布评论员 常瑞民